# Ferranti DATA CONVERTER TECHNICAL HANDBOOK

Ferranti Electronics Limited

#### ©FERRANTI LTD. 1981

The copyright in this work is vested in Ferranti Limited and this document is issued for the purpose only for which it is supplied. No licence is implied for the use of any patented feature. It must not be reproduced in whole or in part, or used for tendering or manufacturing purposes except under an agreement or with the consent in writing of Ferranti Ltd. and their only on the condition that this notice is included in any such reproduction. Information furnished is believed to be accurate but no liability in respect of any use of it is accepted by Ferranti Ltd.

FERRANTI ELECTRONICS LIMITED

FIELDS NEW ROAD, CHADDERTON, OLDHAM OL9 8NP Tel: 061-624 0515 & 6661 Telex: 668038

Ferranti GmbH, Widenmayerstrasse 5, D8000-Munich-22, West Germany Tel: 089-293871 Telex: 523980

Ferranti Electric Inc., 87 Modular Avenue, Commack, N.Y. 11725, U.S.A. Tel: 516-543 0200 TWX: 510 226 1490

Interdesign Inc. (a Ferranti company), 1255 Reamwood Avenue, Sunnyvale, California 94086, U.S.A. Tel: 408-734 8566 TWX: 910 339 9374

# DATA CONVERSION HANDBOOK

CONTENTS

|            | de Convertara                                               |         |

|------------|-------------------------------------------------------------|---------|

| anding Con |                                                             | . 21    |

| DA         | TA CONVERTERS                                               | 25      |

|            | Guide – A to D Converters                                   |         |

|            |                                                             | 3).—3   |

|            |                                                             |         |

|            |                                                             |         |

|            | 8-Bit Latched Input Monolithic D to A Converter             | 81 - 70 |

|            |                                                             | 71 - 71 |

|            | 10-Bit Successive Approximation Monolithic A to D Converter |         |

|            |                                                             |         |

|            | 31 Digit DVM Logic Subsystem                                |         |

| ZNA216     |                                                             |         |

|            |                                                             | 127-140 |

|            |                                                             |         |

# **DATA CONVERSION HANDBOOK**

# CONTENTS

| S | ection            |                  |         | 2 75           |                  |         |         |        | Page      |

|---|-------------------|------------------|---------|----------------|------------------|---------|---------|--------|-----------|

| 1 | Digital to Analog | ue Converters    |         | 7.             |                  |         |         |        | 1 – 8     |

| 2 | Analogue to Dig   | ital Converters  | rerte   |                |                  |         |         |        | 9 – 20    |

| 3 | Companding Co     | nverters         | hensiv  | e Harra        | nd fen           | ga bi   | menoli  | thic I | 21        |

| 4 | Quality Assurance | e Programme      | solutio | ona to a       | a wide           | variety | rol dat | a con  | 22        |

| 5 | Product Selectio  | n Guide – D to A | Conve   | erters         | end ex           | tende   | s. que  | ardiy  | 29        |

| 6 | Product Selectio  | n Guide – A to D | Conve   | erters         | cost o           | omverb  | ors, mi | Crops  | 30        |

| 7 | Product Data      |                  |         |                |                  |         |         |        |           |

|   | ZN425             | 8-Bit Monolith   | ic D to | A/A to         | D Co             | nverte  | r       | food   | 31 – 38   |

|   | ZN426             | 8-Bit Monolith   | ic D to | A Con          | verter           | and no  | 100 0   |        | 39 – 44   |

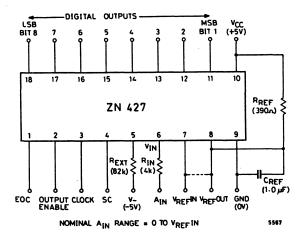

|   | ZN427             | 8-Bit Successiv  | ve Appr | roximat        | tion A           | to D C  | onvert  | er     | 47 – 59   |

|   | ZN428             | 8-Bit Latched    | Input N | /lonolit       | hic D t          | OAC     | onvert  | er     | 61 - 70   |

|   | ZN429             | 8-Bit Monolith   | ic D to | A Cor          | verter           |         |         |        | 71 – 76   |

|   | ZN432             | 10-Bit Success   | sive Ap | proxim<br>Mond | ation<br>olithic | A to D  | Conv    | erter  | 77 – 86   |

|   | ZN433             | 10-Bit Tracking  | g Mond  | olithic A      | A to D           | Conve   | erter   |        | 87 – 96   |

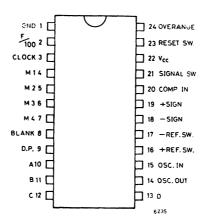

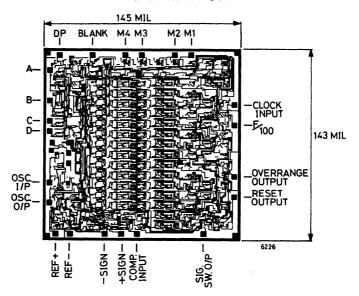

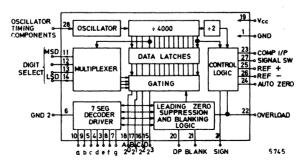

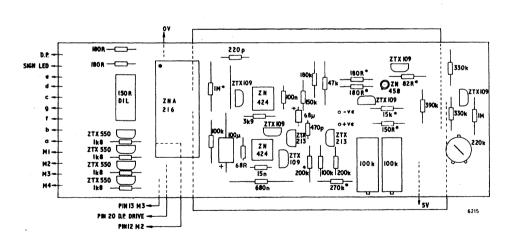

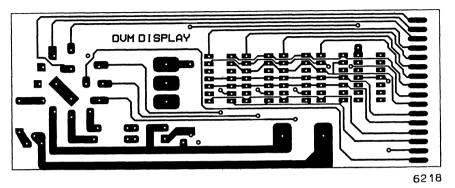

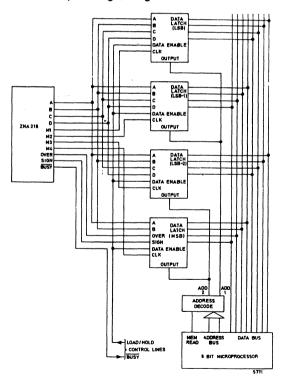

|   | ZNA116            | 3½ Digit DVM     | Logic S | Subsys         | tem              |         |         |        | 97 – 110  |

|   | ZNA216            | 33 Digit DVM     | Logic S | Subsyst        | tem              |         |         |        | 111 – 125 |

|   | ZNPCM             | Single Channe    | I Code  |                |                  |         |         | 1      | 127 – 140 |

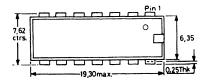

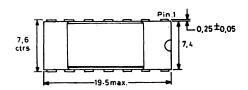

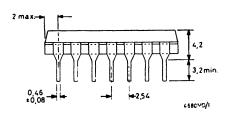

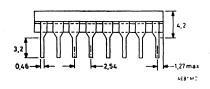

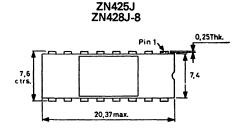

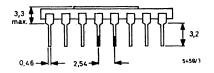

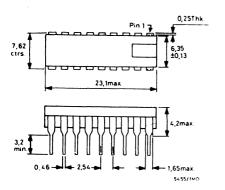

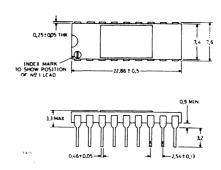

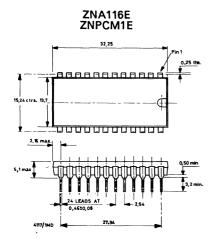

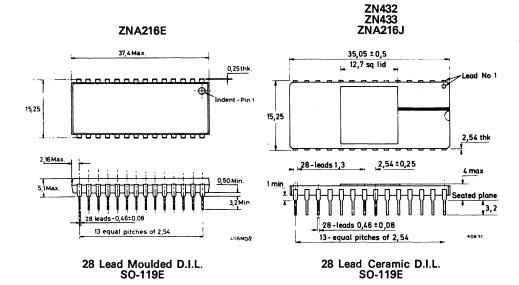

| 8 | Package Details   | /.:              |         |                |                  |         |         | 1      | 141 – 143 |

# INTRODUCTION

# **Monolithic Data Converters**

This handbook describes the comprehensive Ferranti range of monolithic I.C. data converters, which offer cost-effective solutions to a wide variety of data conversion problems.

This range, which is constantly being improved and extended, currently offers a choice of 40 different versions, including low-cost converters, microprocessor compatible A to D and D to A converters, dual slope DVM logic subsystems and a single channel CODEC.

The introductory section of this handbook is intended as a guide to the fundamental principles of data conversion and as an aid to understanding the terms used in converter specifications, which will enable the user to choose the most appropriate device for a particular application. The second section contains product data on the full range of Ferranti data conversion I.Cs.

# 1. DIGITAL TO ANALOGUE CONVERTERS

A Digital to Analogue converter (DAC) is a device which converts a digital data input into a corresponding analogue output. This output usually takes the form of a voltage or current.

# 1.1 Ideal Output Characteristics

If a unipolar voltage output and normal binary input coding are assumed, then the ideal transfer function of a linear DAC may be written as:

$$V_{out} = V_{FS} (B_1.2^{-1} + B_2.2^{-2} + B_3.2^{-3} + \dots + B_n.2^{-n})$$

where  $B_1$  is the most significant bit input (MSB) and  $B_n$  is the least significant bit input (LSB). Bits 1 to n can each assume a value of '1' or '0'. The number of bit inputs a DAC possesses is known as the RESOLUTION of the converter.

The smallest increment of output voltage is that contributed by the LSB and is equal to  $V_{\rm FS}.2^{-n}$ .

The terms 'MSB', 'LSB' etc., are frequently used interchangeably to describe either the digital input or the corresponding analogue output.

The maximum output from a DAC is known as full-scale output ( $V_{\text{FSO}}$ ).

It occurs when all inputs are '1' and is equal to  $V_{FS}\left(\frac{(2^n-1)}{2^n}\right)$ . For example the maximum output of a 3-bit DAC is  $\frac{7}{8}V_{FS}$ .

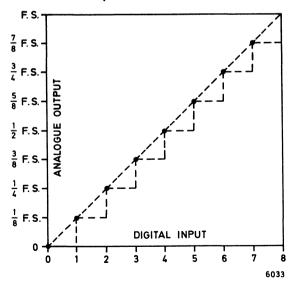

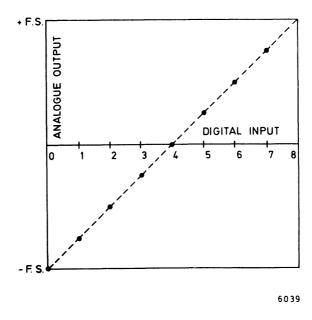

The transfer function graph of an ideal 3-bit DAC is shown in figure 1. For each of the 8 input codes there exists a discrete analogue output

Fig. 1. Transfer Characteristic of Ideal 3-bit DAC

level, represented by a point on the graph. It should be emphasised that the transfer characteristic is not a continuous function and it is, therefore, not strictly correct to join the points with a continuous line, since this would imply that non-integral input codes and corresponding levels existed. However, a straight line is often drawn between zero and full scale to represent the 'ideal' transfer function on which all the points should lie.

Similarly, if the input code of a DAC is incremented using, say, a binary counter and clock generator, then the analogue output will be a staircase waveform. DAC transfer functions are frequently drawn as a staircase, since this is a convenient way of illustrating various errors that may occur in a DAC. However, such a graph is, strictly speaking, a plot of analogue output v. time rather than output v. input code.

#### 1.2 Practical DAC Circuits

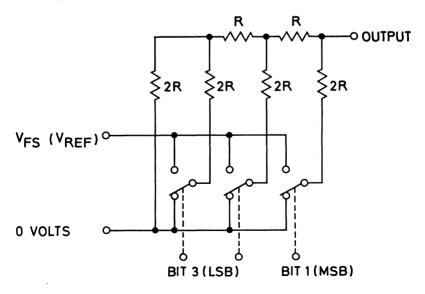

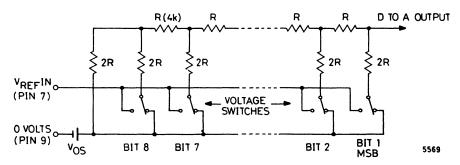

Figure 2 shows an example of a 3-bit DAC circuit based on a voltageswitching R-2R ladder network, a technique widely used in Ferranti converters.

Each 2R element is connected either to 0 volts or  $V_{FS}$  ( $V_{REF}$ ) by transistor switches. Binary weighted voltages are produced at the output of the R-2R ladder, the value being proportional to the digital input number.

Fig. 2. 3-bit Voltage Switching DAC

For example, it is fairly easy to see that if bit 1 is '1' and bits 2 and 3 are '0' then an output of  $V_{FS/2}$  is produced. This is because the resistance of the ladder looking from the output through the first R is 2R, which forms a 2:1 attenuator with the 2R in series with the MSB switch. Output voltages for other input codes can similarly be calculated, and it can be seen that the ladder may be extended to any number of bits.

The voltage switching ladder technique is used in the ZN426, ZN428 and ZN429 series of D to A converters and also in the ZN425 dual-purpose A to D/D to A converter.

#### 1.3 D to A Parameters and Definitions

#### 1.3.1 Converter Errors

The ideal DAC assumes that all the resistors are perfectly matched and that the switches have zero resistance. In a practical converter this will not be the case and various errors will occur in the output.

#### 1.3.2 Monotonicity

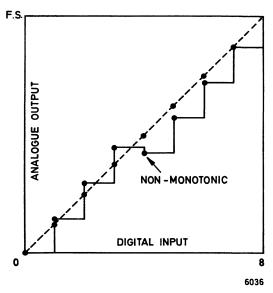

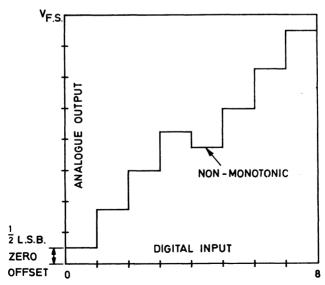

When the input code of a DAC is increased in 1 LSB steps the analogue output of the DAC should also increase, staircase fashion. If the output always increases in this manner then the DAC is said to be monotonic, i.e. the output is a single-valued function of the input. If, due to errors in the bit weighting, the output of the DAC decreases at any step, as shown in figure 3, then the DAC is said to be non-monotonic.

Fig. 3. Non-monotonic DAC

#### 1.3.3 Offset (Zero Error)

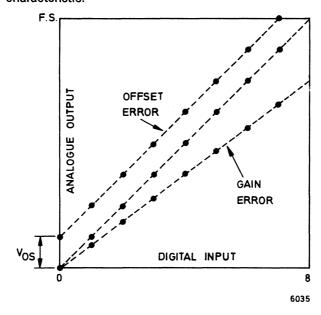

Assuming unipolar operation and normal binary coding, when the input code is zero then the DAC output should also be zero. However, due to package lead resistances and offset voltages in the switches this will not be the case, and a small output offset may exist. This has the effect of shifting the transfer function so that it no longer passes through zero, as shown in figure 4.

#### 1.3.4 Gain Error

If the reference voltage of a DAC is exactly the nominal value then the transfer characteristics of the converter should follow the ideal straight line. However, due to imperfections in the converter the transfer function may diverge from this line, as shown in figure 4. This error is known as gain error and is the difference between the slope of the actual transfer characteristic and the slope of the ideal transfer characteristic.

Fig. 4. Illustrating Offset and Gain Errors

#### 1.3.5 Linearity Errors

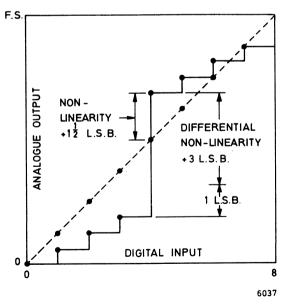

Offset and gain errors may be trimmed out so that the end points of the transfer characteristic lie at zero and  $V_{\rm FSO}$ . However, even when this has been done, some or all of the intermediate points may not lie on the 'ideal' line. These errors, which cannot be trimmed out, are known as linearity errors.

#### 1.3.6 Non-Linearity (Linearity Error)

This is the maximum amount, given either as a percentage of full scale or a fraction of an LSB, by which any point on the transfer characteristic deviates from the ideal straight line passing through zero and  $V_{FSO}$ . Non-linearity is illustrated in figure 5. A linearity error within the range  $\pm \frac{1}{2}$  LSB assures monotonic operation. Note however that the converse is not true and a DAC may still be monotonic with large linearity errors, which is also shown by figure 5.

#### 1.3.7 Differential Non-linearity

This is the maximum difference, specified as a fraction of an LSB, between the actual and ideal size of any one LSB analogue increment. This can be seen as an error in the step height of a DAC staircase. A positive value of differential non-linearity means that the step height is larger than nominal, whilst a negative value means that it is smaller than nominal. If it is more negative than -1 LSB then the DAC is non-monotonic. However, positive differential non-linearity may assume any value and a DAC can still be monotonic, as shown in figure 5.

Fig. 5. Illustrating Linearity Errors

#### 1.3.8 Resolution

As stated earlier, the resolution of a DAC is simply the number of bit inputs that a DAC possesses, which indicates the smallest analogue increment that the converter can produce as a fraction of  $V_{FS}$ , e.g. 8 bits = 1 part in  $2^8$  (256). Resolution implies nothing about the accuracy of a DAC, which is defined by linearity and other errors.

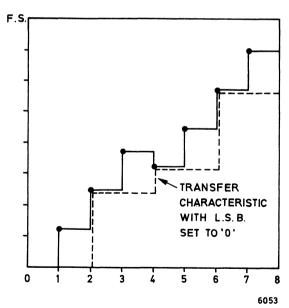

#### 1.3.9 Useful Resolution

If an n bit DAC has a differential non-linearity of say -1.5 LSB then it is non-monotonic. However, if the LSB input is made permanently '0' then the DAC becomes an n-1 bit device with an LSB equal to twice the original LSB. The differential non-linearity error thus becomes -0.75 (new) LSB and the device is monotonic at a resolution of n-1 bits. This is illustrated in figure 6, which shows the transfer characteristic of a 3-bit DAC that has a useful resolution of 2 bits

Due to manufacturing tolerances a proportion of n-bit converters will have only n-1 or n-2 bit useful resolution. In applications not requiring n —bit useful resolution these reduced resolution versions offer a significant price advantage. The useful resolution of Ferranti DACs is guaranteed over their full operating temperature range.

Fig. 6. Non-monotonic 3-bit DAC With a Useful Resolution of 2 bits

1.3.10 Settling Time is the time taken after a transition of the input code for the output of a DAC to settle to within  $\pm \frac{1}{2}$  LSB of its final value. This varies depending on which bits are being changed. It may be specified for a change of 1 LSB which generally gives the most optimistic (fastest) figure. More conservative figures are given by the most major transition (where the MSB changes in one direction and all other bits change in the opposite direction, e.g. 011111111 to 10000000 or vice versa) or by a change from all bits off to all bits on (00000000 to 11111111) or vice versa.

#### 1.4 Bipolar Operation

The discussion so far has been concerned only with DACs producing a single polarity (usually positive) output voltage. In some applications a bipolar (both positive and negative) output range may be required.

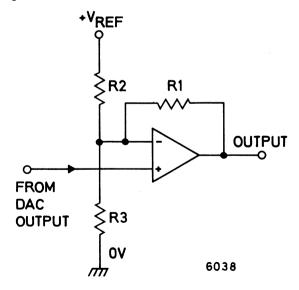

This can be achieved by adding a negative offset of  $\frac{\mathsf{V}_{\mathsf{REF}}}{2}$  to the analogue output, as shown in figure 7. For all input codes where the MSB is '0' the output voltage is then negative, and for output codes where the MSB is '1' the output voltage is positive. Where the input coding is normally binary but the output voltage is offset by  $\frac{-\mathsf{V}_{\mathsf{REF}}}{2}$  then the input code is referred to as offset binary.

The transfer function of a 3-bit DAC with offset binary coding is shown in figure 8.

Fig. 7. Bipolar Operation of a DAC

Fig. 8. Bipolar Operation of a 3-bit DAC

# 2. ANALOGUE TO DIGITAL CONVERTERS

An analogue to digital Converter (ADC) is a device which converts an analogue input into a corresponding digital output code.

# 2.1 Ideal Output Characteristics

Assuming a unipolar input voltage and binary coded output, the transfer function of an ideal n-bit ADC is given by:

$$V_{ES} (B_1.2^{-1} + B_2.2^{-2} + .... + B_n.2^{-n}) = V_{in} \pm \frac{1}{2} LSB$$

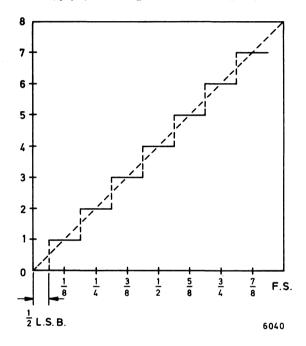

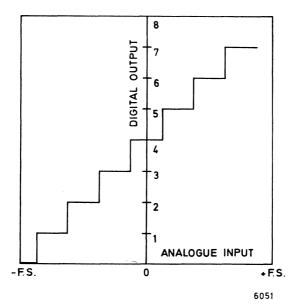

Fig. 9. Ideal 3-bit ADC Transfer Characteristic

The transfer function of an ideal 3-bit ADC is shown in figure 9. In this case there are 8 digital output codes corresponding to the 8 input codes of a DAC. However, unlike the analogue output of a DAC, the analogue input of an ADC can vary continuously, which means that each digital output code, with the exception of 0 and 7, exists over an analogue increment of 1 LSB. The zero of an ADC is usually trimmed so that the transitions between codes occur  $\frac{1}{2}$  LSB on either side of the nominal analogue input for a particular code. For example, the nominal input for output code 2 is  $\frac{1}{4}$  V<sub>FS</sub>. The transition from 1 to 2 occurs at  $\frac{3}{16}$  V<sub>FS</sub> and the transition from 2 to 3 occurs at  $\frac{5}{16}$  V<sub>FS</sub>.

As with a DAC, an 'ideal' straight line may be drawn through the transfer characteristic of an ADC.

#### 2.2 Practical A to D Conversion Methods

There are many methods of performing an analogue to digital conversion. Although not all of these methods are used in the current range of Ferranti A-D converters, they are all, nonetheless, mentioned for the sake of completeness.

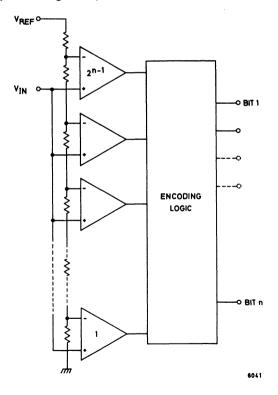

#### 2.2.1 Parallel (Flash) Conversion

In an n-bit parallel converter (Fig. 10) a resistor ladder is used to generate  $2^n$  –1 voltage levels from 1 LSB to  $(2^n$  –1) × LSB which are fed to the reference inputs of  $2^n$  –1 voltage comparators. The analogue input signal is fed to the second input of each comparator, and is thus compared simultaneously with each of the  $2^n$  –1 voltage levels. At the point in the comparator chain where the reference voltage exceeds the input voltage the comparator outputs will change over from low to high. The comparator outputs are encoded into whatever digital output coding is required.

Fig. 10. Parallel A-D Converter

Since the only delays involved in the conversion are the propagation delay of one comparator plus the logic propagation delays, parallel converters are very fast and may perform in excess of 10 million conversions per second. However, due to the large number of comparators required (63 for a 6-bit converter, 255 for an 8-bit converter) they are expensive to produce. Applications include digital video systems, digital storage oscilloscopes and radar data processing.

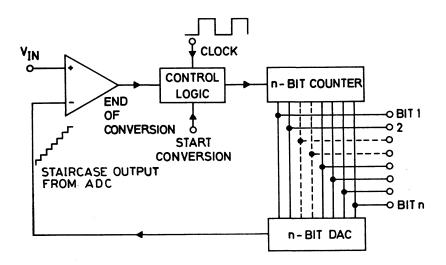

#### 2.2.2 Staircase and Comparator

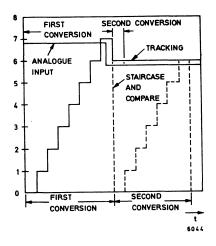

In this type of ADC the input code of a DAC is incremented by a binary counter to give a staircase waveform, as shown in figure 11. This is compared with the analogue input and when the staircase exceeds the analogue voltage the comparator output changes state and stops the clock. The count reached by the binary counter is thus the ADC output code. This method of A to D conversion is relatively simple and cheap, but is also relatively slow, requiring  $2^n - 1$  clock pulses for a full scale conversion, where n is the number of bits. This conversion method is used in the ZN425 series of dual-purpose D-A/A-D converters.

6042

Fig. 11. Staircase (Ramp) and Compare ADC

#### 2.2.3 Tracking Converters

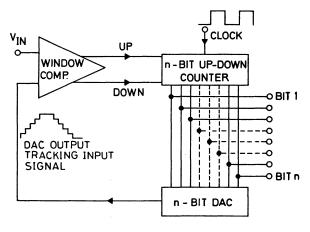

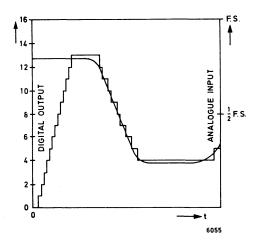

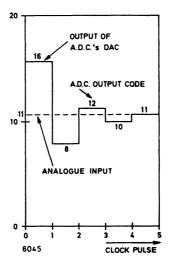

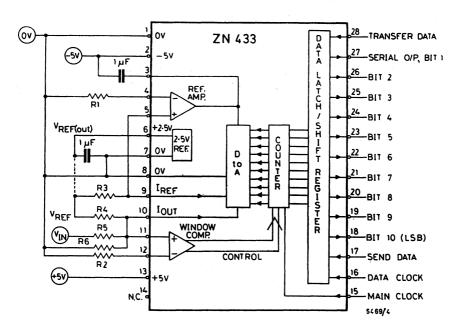

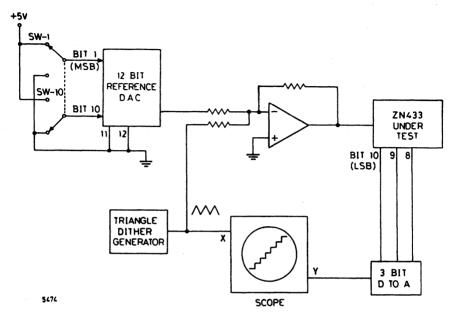

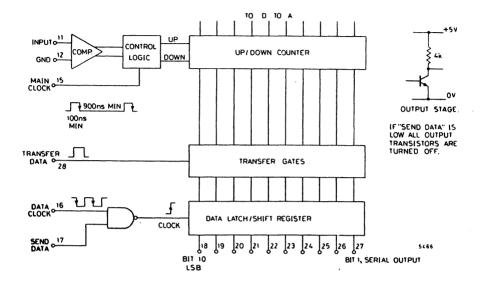

As its name implies, a tracking converter can follow changing analogue inputs. The principle operation is similar to that of the staircase and compare type of converter, but it uses an up/down counter and a window comparator, as shown in figure 12. When the DAC output is less than the analogue input the comparator instructs the counter to count up and the DAC output thus increases. If the DAC output is greater than the analogue input the comparator causes the counter to count down, thus decreasing the DAC output. When the DAC output is equal to the analogue input  $+\frac{1}{2}$  LSB, the input is within the 'window' of the comparator and the counter is stopped. This is illustrated in figure 13. A tracking converter has speed advantages over a staircase and compare type, since the counter of the latter type can only count up, and must therefore be reset between conversions. In the case of a tracking converter, once it has performed an initial conversion starting from zero, any subsequent conversions require only that number of clock pulses necessary to track any increase or decrease in input voltage.

Fig. 12. Tracking ADC

As an extreme example consider an analogue input that changes from  $V_{FSO}$  to  $(V_{FSO}-1\ LSB)$ . The staircase and compare converter will require  $2^n-1$  clock pulses for the first conversion and  $2^n-2$  clock pulses for the second conversion. The tracking converter on the other hand, will require  $2^n-1$  clock pulses for the first conversion but only one clock pulse for the second conversion. This is illustrated in figure 14.

6043

Fig. 13. Operation of Tracking ADC

Fig. 14. Comparison of ramp and compare and tracking ADCs

In general it can be said that a tracking converter will follow signals whose rate of change is less than  $\pm 1$  LSB  $\times$  clock frequency. If this condition is met there is no need to use a sample-and-hold circuit on the analogue input.

A tracking technique is used in the ZN433 series of converters.

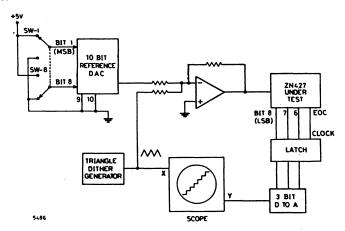

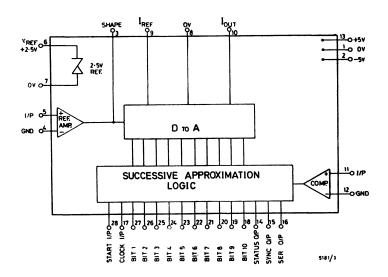

#### 2.2.4 Successive Approximation Converters

The operation of a staircase and compare ADC is analogous to weighing, say an 11 gramme weight, on a balance by adding one gramme weights until the scale tips, which is clearly a very slow method. A faster procedure, known as successive approximation, uses weights of 16, 8, 4, 2 and 1 grammes. The 16 gramme weight is tried first and is discarded because it tips the scale. The 8 gramme weight is tried next, and is left on the pan. Next the 4 gramme weight is tried and discarded, and the 2 and 1 gramme weights are tried and retained. The final result is the sum of the weights remaining on the scale pan, and the operation has taken 5 'cycles' as opposed to 11 'cycles' for the staircase and compare method.

The principle of a successive approximation ADC is identical. The MSB of a DAC is first set to '1' and the output is compared to the analogue input. If it is greater than the input the MSB is reset to '0', otherwise it is left at '1'. The next bit is then set to '1' and the DAC output is again compared to the analogue input. Again it is either reset or left at '1' depending on the result of the comparison. This procedure is repeated for every bit down to the LSB, and the final input code to the DAC is the output code of the ADC. A successive approximation cycle is illustrated in figure 15.

Fig. 15. Operation of a Successive Approximation ADC

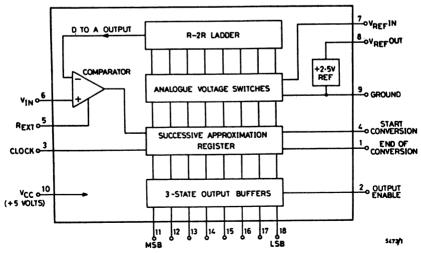

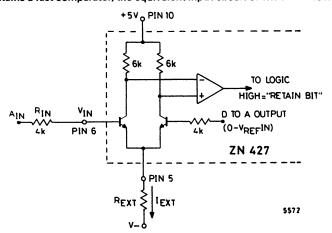

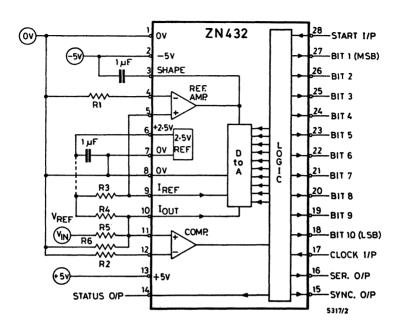

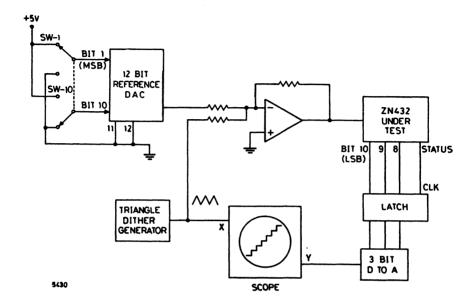

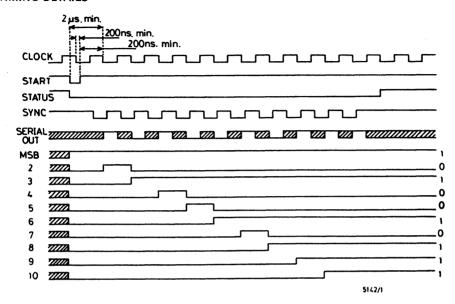

Successive approximation is used in the ZN427 and ZN432 series of converters.

#### 2.2.5 Dual Slope Converters

Dual slope integration is one of the slowest methods of A to D conversion, but it offers high resolution at a modest cost.

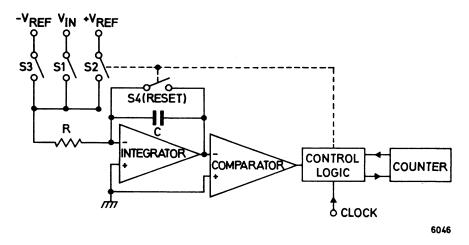

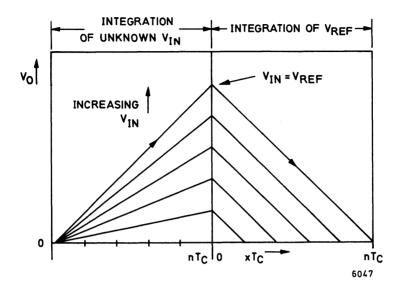

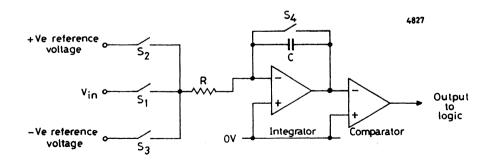

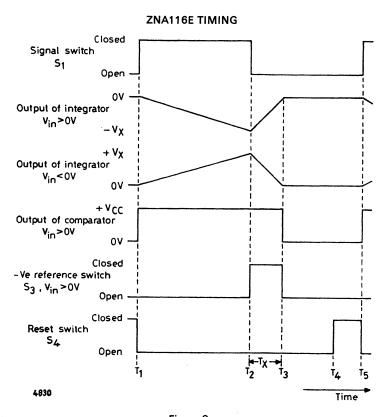

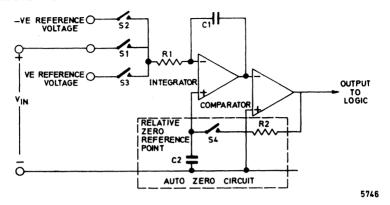

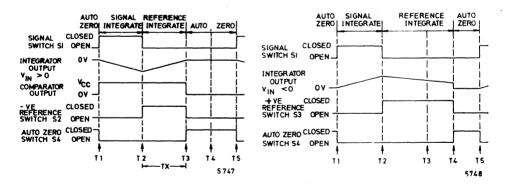

A block diagram of a dual-slope converter is shown in figure 16. It operates in the following manner: Switch S1 is closed by the control logic, S4 is opened and the input voltage is integrated for n clock periods, where n is usually the maximum count of the counter. At the end of this time the integrator output voltage,  $V_0$ , is  $\frac{-V_{in} \ n \ T_c}{RC}$  where  $T_c$  is the clock period. This is shown in figure 17.

Fig. 16. Dual-Slope ADC

During this period the polarity of the input signal is detected by the comparator. At the end of the integration period S1 is opened and, depending on the polarity of  $V_{\rm in}$ , either S2 or S3 is closed to connect the integrator to a reference voltage of opposite polarity to  $V_{\rm in}$ . The counter is now allowed to count from zero until the integrator output reaches 0 volts, when the comparator output changes state and the counter is stopped. Since the integration is over the same voltage range ( $V_{\rm O}$ ),  $V_{\rm O} = \frac{-V_{\rm REF} \, x \, T_{\rm C}}{RC}$ , where x is the count

Fig. 17. Operation of Dual-Slope ADC

reached by the time the integrator output crosses zero. Thus

$$\frac{V_{in}.n~T_c}{RC} = \frac{V_{REF}~x~T_c}{RC}$$

or  $x = \frac{V_{in}.n}{V_{REF}}$

Since n and  $V_{REF}$  are both fixed the output count is proportional to the input voltage. Since both the first and second integrations occur under identical conditions the converter is unaffected by any long-term variations in  $T_c$ , R or C, as demonstrated by the disappearance of these terms from the final equation. The only factors affecting the accuracy of the converter are (1) the stability of  $V_{REF}$  (2) the stability of the 'on' resistance of S1 to S3 and (3) drift in the integrator and comparator op-amps. These effects can be minimised by careful design.

Dual slope converters are generally used where high resolution and low cost are more important than speed, for example in digital voltmeters.

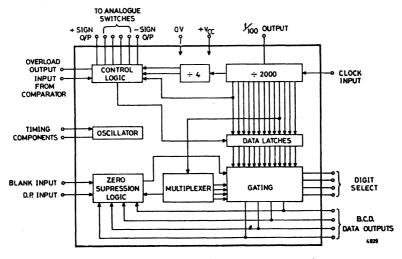

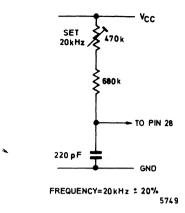

The ZNA116 and ZNA216 are DVM logic subsystems containing the clock, counter and all control logic necessary for dual slope converter or DVM.

#### 2.3 A to D Parameters and Definitions

#### 2.3.1 A to D Converter Errors

Like DACs, practical ADCs are subject to a number of error sources, and since most ADCs contain a reference DAC, many of these error sources are the same for both types of converter.

#### 2.3.2 Quantising Error (Uncertainty)

Quantising error is an ADC specification that has no counterpart in DAC specifications. For each input code of a DAC there is a unique analogue output level, but for any ADC output code there is a 1 LSB range of analogue input levels. It is thus not possible to tell from the output code the precise value of the analogue input level, there being a quantising error or uncertainty of  $\pm \frac{1}{2}$  LSB. Since all ADCs have this inherent quantising error the parameter is frequently not quoted in specifications.

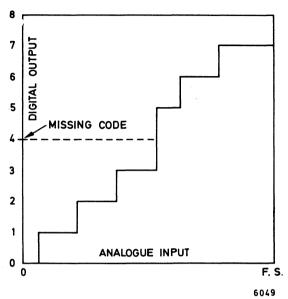

#### 2.3.3 Missing Codes

Missing codes are perhaps best explained by considering the operation of a staircase and compare type 3-bit ADC which has a non-monotonic DAC, as shown in figure 18. The reference DAC exhibits non-monotonicity at input code 4, i.e. step 4 of the staircase decreases. There is thus no way in which the counter can be stopped at this code. If the analogue input is less than the DAC output for code 3 then the comparator will stop the counter before 4 is reached. If the analogue input is greater than output 3 it must also be greater than output 4, so the comparator will not change state at code 4.

Fig. 18. Non-monotonic DAC used in an ADC

Output code 4 will thus never appear and is known as a 'missing' code. The transfer function of an ADC with a missing code is shown in figure 19.

Fig. 19. ADC With Missing Code

#### 2.3.4 Zero Transition

As explained earlier, the zero of an ADC is usually trimmed so that the output transition from 0 to 1 occurs at an input level corresponding to  $\frac{1}{2}$  LSB, i.e.  $\frac{1}{2}\frac{V_{FS}}{2^n}$ . However, as supplied the reference DAC of an ADC I.C. will not have the  $\frac{1}{2}$  LSB offset necessary to achieve this. The zero transition will thus occur at 1 LSB plus the DAC zero error, plus the comparator offset voltage. These three parameters are frequently

#### 2.3.5 Gain Error

This is the difference between the slope of a line drawn between the actual zero and full scale transition points and that of a line drawn through the ideal transition points.

lumped together as the (untrimmed) zero transition of the ADC.

# 2.3.6 Non-linearity (Linearity Error)

Non-linearity is the maximum amount by which any actual transition points deviates from the corresponding ideal transition point. It is specified as a percentage of full-scale or a fraction of an LSB. A linearity error of less than  $\pm \frac{1}{4}$  LSB assures no missing codes.

#### 2.3.7 Differential Non-linearity

This is the maximum difference between any 1 LSB increment of the analogue input and the ideal size of an LSB increment  $\frac{V_{FS}}{2^n}$ . Differential non-linearity of less than 1 LSB guarantees no missing codes.

#### 2.3.8 Resolution

The resolution of an ADC is simply the number of bit outputs that the converter possesses. As with a DAC, resolution implies nothing about the accuracy of a device.

#### 2.3.9 Useful Resolution

Useful resolution is the resolution (number of bits) at which an ADC has no missing codes, which for Ferranti ADCs is guaranteed over the operating temperature range. As with DACs, an n-bit ADC may have a useful resolution less than n bits, for reasons previously explained.

#### 2.3.10 Conversion Time

The time taken for an ADC to perform a complete conversion is known as the conversion time. For successive approximation converters conversion time is fixed by the number of bits and the clock frequency. However, for other types, conversion time may vary with input voltage. For example, a ramp and compare ADC requires  $2^n - 1$  clock pulses for a full scale conversion but only one clock pulse for a one bit conversion. It is thus important to check exactly what is being specified.

#### 2.4 Bipolar Operation

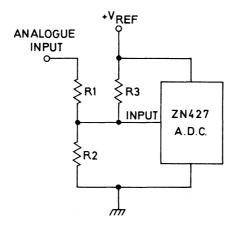

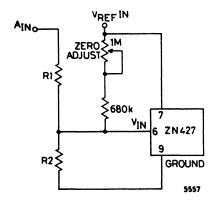

As with a DAC, an ADC may be used for bipolar operation. Taking the ZN427 as an example the input is offset by  $\frac{+V_{REF}}{2}$  so that the input voltage presented to the ADC is always positive, even with negative input voltages down to  $\frac{-V_{REF}}{2}$ . The principle of offsetting an ADC input is illustrated in figure 20, whilst the transfer function of a 3 bit bipolar ADC is shown in figure 21. In this case the **output** coding is known as offset binary.

Fig. 20. Bipolar Operation of an ADC

6050

Fig. 21. Bipolar Transfer Characteristic of an ADC

# 3. COMPANDING CONVERTERS

Unlike conventional DACs whose outputs are invariably linearly proportional to the digital number at the inputs, a companding DAC has an output that is intentionally non-linear with respect to its digital input.

In general, assuming a constant reference, a companding DAC's output is an exponential function of the digital input. A small change in the digital input, when it is near zero, produces a very small change in the analogue output. As the digital input goes towards full scale, the same digital change produces a progressively larger change in the analogue output.

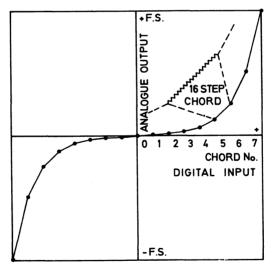

A companding DAC's transfer function is an eight segment piecewise linear approximation to the ideal exponential characteristic. Within each segment – also called a 'chord' – the transfer function is linear. However, with the sizes of the analogue-output steps differing by a factor of two in adjacent chords, the chords have slopes that approximate the non-linear function. Each chord contains 16 steps making a total of 128 steps in all from zero to full scale.

Companding DACs usually relate to 7-bit resolution with an additional sign bit making it an 8-bit input device. The sign bit is the MSB, the next three most significant bits selecting the chord and the final four bits the steps within the chord. The final transfer characteristic is shown in figure 22. The ADC companding function is similar in nature, with the transfer characteristic being the inverse of that shown for the DAC.

Fig. 22. Transfer Function of a Companding DAC

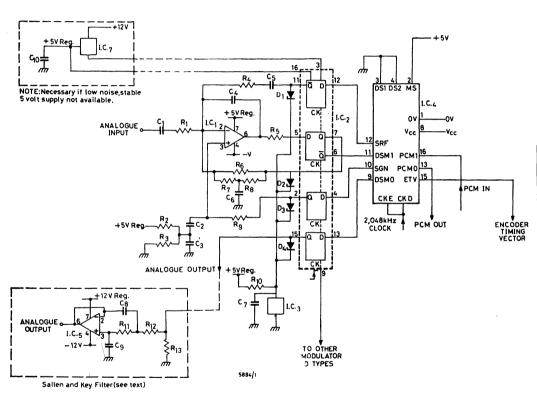

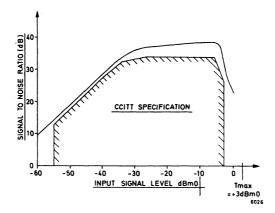

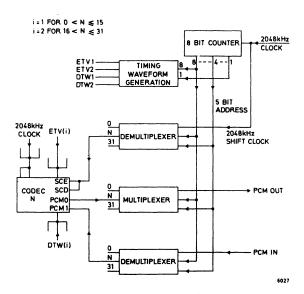

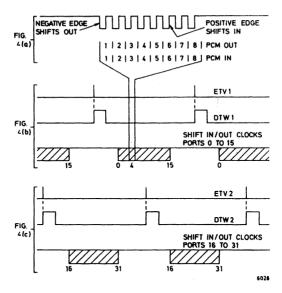

The most popular application areas for this type of converter are single channel code conversion of voice signals in telephone exchange networks. The Ferranti ZNPCM1 Codec performs such a function using some innovative circuit techniques. The companding is performed in all digital circuitry using an intermediate delta-sigma modulation function.

# 4. QUALITY ASSURANCE PROGRAMME

The quality control procedures at Ferranti Electronics Limited are based on British Standard 9000, the relevant documents being:

BS 9002: Qualified products list for electronic components of assessed quality (including list of approved firms).

BS 9400: Integrated electronic circuits and micro-assemblies of assessed quality.

BS 9450: Custom-built integrated circuits of assessed quality.

BS 6001: Sampling procedures and tables for inspection by attributes.

The quality emphasis at Ferranti is on process control (as indicated by the use of many monitors and audits) in addition to gate inspections. This philosophy is consistent with building in quality and reliability rather than attempting solely to screen for it.

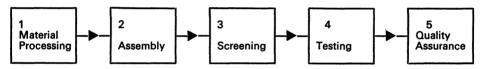

There are five basic stages in the manufacture of Ferranti data converters, as shown below:

Each of these stages has associated with it a number of quality control checks to ensure that components will meet the standards required by the most stringent environments encountered in the field of electronics.

#### 4.1 Processing

The technology used to fabricate the Ferranti range of data converters is a five mask bipolar process (see publication ref. ESA 480673). This process is used to manufacture the whole range of Ferranti LSI products, but is especially suited to converter products since it allows analogue and digital circuits to be fabricated on the same chip, with good yields and high packing densities. The process has full BS 9450 capability approval and is the first bipolar process in the U.K. to receive such approval.

# 4.2 Assembly

Ferranti data converters are available in either moulded or hermetically sealed ceramic dual in-line (DIL) packages (though certain types are available only in ceramic package). The assembly flow-charts for both types of package are shown in Table 1. All products are manufactured by the same routes and using the same techniques as BS 9000 approved products.

# TABLE 1

| PLASTIC                        | CERAMIC                        |

|--------------------------------|--------------------------------|

| Wafer                          | Wafer                          |

| Dice Preparation               | Dice Preparation               |

| Dice Inspection                | Dice Inspection                |

| Alloy                          | QC Lot Acceptance              |

| Bond                           | Alloy                          |

| Pre-cap Inspection             | Bond                           |

| QC Lot Acceptance              | Pre-cap Inspection             |

| Mould                          | QC Lot Acceptance              |

| Post Mould Cure(5 Hrs. at 18   | 5°C) Bake 1 hour at 200°C      |

| Tin plate                      | Encapsulate                    |

| Visual Quality & Solderabili   | ty Fine Leak Test              |

| Part Mark                      | Gross Leak Test                |

| Part Mark Quality & Durabili   | ty 🖒 Part Mark                 |

| Physical Inspection            | Part Mark Quality & Durability |

| QC Lot Acceptance              | Physical Inspection            |

| Electrical Test                | QC Lot Acceptance              |

| $\nabla$                       | Electrical Test                |

| arehouse                       | Warehouse                      |

| Many Objective Drawns Ass      |                                |

| <b>Key</b> :  ○Product Process | % Inspection Sampling 6083     |

# 4.3 Screening

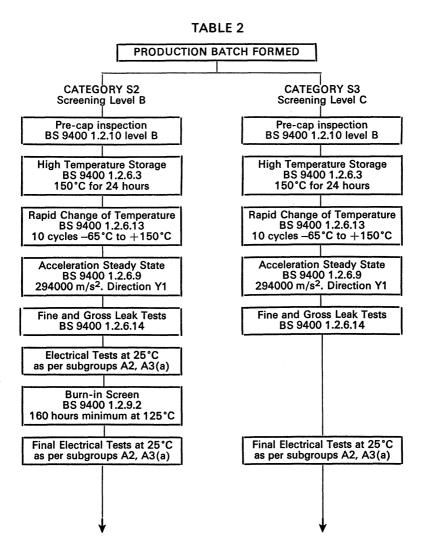

In addition to the standard manufacturing cycle, optional screening procedures are available to produce high-reliability products. A full breakdown of the options available, related to their BS 9400 procedures, is shown in Table 2.

# 4.4 Testing

On completion of assembly all devices are subjected to 100% functional and d.c. testing in addition to either an S4, 2.5% sample or 100% check on a.c. characteristics depending on device type. The d.c. tests are inset to tighter limits than those shown on the data sheet in order to ensure that the device will function within the specified conditions over its full operating temperature range.

In addition to the 100% test already described, devices manufactured to commercial specifications also undergo sample tests to the AQLs in Table 3, including the temperature extreme tests mentioned above.

TABLE 3

| Inspected Parameter                                                             | Inspection Level | AQL   |

|---------------------------------------------------------------------------------|------------------|-------|

| Visual & Mechanical including major external workmanship and marking permanency | ı                | 1%    |

| Function                                                                        | 11               | 0.15% |

| Major Electrical Parameters at T <sub>amb</sub> = 25°C                          | II               | 0.65% |

| Major Electrical Parameters over operating temperature range                    | II               | 2.5%  |

#### 4.5 Quality Assurance

Despite all the measures taken to ensure that commercial product is of a high standard it is inevitable that certain market sectors will require a higher level of quality assurance. These market sectors are predominantly military and telecommunications orientated.

Wherever devices are supplied to these more stringent QA requirements they are re-routed at the end of the assembly cycle through our QA Bond Department. They are subjected, on a lot-by-lot basis, to a more rigorous examination of ther quality using methods laid down in BS 9000 or its equivalent for the specification concerned.

In addition to lot-by-lot testing, long term life testing of product is performed continually. This enables constant monitoring of process stability and any undesirable deviations from the norm are quickly brought to light so that corrective measures may be implemented.

# 4.6 Acceptable Quality Levels

As explained earlier the procedures and manufacturing techniques used by Ferranti are consistent with producing an inherently reliable product rather than screening out unreliable product. This is achieved by careful process control combined with numerous gate inspections.

In order for such a system to be effective it is necessary to implement a sampling procedure where the sample size and inspection levels of the various stages are adequate to assure satisfactory quality of the end product whilst remaining cost effective. This can be achieved only after a long history of semiconductor manufacture, which gives an intimate knowledge of the problems likely to arise at each stage of manufacture, and the best methods of inspecting for them.

The sampling procedures used by Ferranti are those outlined in BS 6001. The Acceptable Quality Level (AQL) is the maximum percentage of defective devices that can, for the purposes of inspection, be considered satisfactory as a process average.

The AQL sample size codes and sampling plan used by Ferranti are reproduced in tables 4 and 5.

TABLE 4

SAMPLE SIZE CODE LETTERS

| Lot or batch size |       |        |     | Spe<br>spection | cial<br>on leve | General<br>inspection levels |   |    |        |

|-------------------|-------|--------|-----|-----------------|-----------------|------------------------------|---|----|--------|

| Lot or            | batch | n size | S-1 | S-2             | S-3             | S-4                          | I | l1 | Ш      |

| 2                 | to    | 8      | Α   | A               | Α               | Α                            | Α | Α  | В      |

| 9                 | to    | 15     | Α   | Α               | Α               | Α                            | Α | В  | С      |

| 16                | to    | 25     | Α   | A               | В               | В                            | В | С  | D<br>, |

| 26                | to    | 50     | Α   | В               | В               | С                            | С | D  | Ε      |

| 51                | to    | 90     | В   | В               | С               | С                            | С | E  | F      |

| 91                | to    | 150    | В   | В               | С               | D                            | D | F  | G      |

| 151               | to    | 280    | В   | С               | D               | E                            | Ε | G  | н      |

| 281               | to    | 500    | В   | С               | D               | E                            | F | н  | J      |

| 501               | to    | 1200   | С   | С               | E               | F                            | G | J  | K      |

| 1201              | to    | 3200   | С   | D               | E               | G                            | н | к  | L      |

| 3201              | to    | 10000  | С   | D               | F               | G                            | J | L  | м      |

| 10001             | to    | 35000  | С   | D               | F               | Н                            | κ | М  | N      |

| 35001             | to    | 150000 | D   | E               | G               | J                            | L | N  | Р      |

| 150001            | to    | 500000 | D   | E               | G               | J                            | М | Р  | a      |

| 500001            | and   | over   | D   | E               | Н               | К                            | N | α  | R      |

# Q A Programme - TABLE 5

|                                               |                | ٠        | ₩ A \                   |                        | <del></del>           |                      |                         |             |

|-----------------------------------------------|----------------|----------|-------------------------|------------------------|-----------------------|----------------------|-------------------------|-------------|

|                                               | 1000           | Ac Re    | 8 # 4<br>E # 4          |                        |                       |                      |                         |             |

|                                               | 650            | Ac Re    | 21 22<br>30 31<br>44 45 | <b></b>                |                       |                      |                         |             |

|                                               | <u> </u>       | <u>چ</u> | 22 25                   | 2 1                    |                       |                      |                         |             |

|                                               | \$             | γ¢       | <b>*</b> # # #          | 3 /                    |                       |                      |                         |             |

|                                               | 250            | Ac Re    | 11 22 22                | 8 \$ \r                |                       |                      |                         |             |

|                                               |                | a.       | 8 10<br>11 14<br>15 21  | 8 % /                  |                       |                      |                         |             |

|                                               | 150            | ¥        | ~ g <del>z</del>        | = = V                  |                       |                      |                         |             |

|                                               | 92             | Ac Re    | s 6<br>7 8<br>10 11     | 2 2 C                  |                       |                      |                         |             |

|                                               | SS             | æ        | + 9 8                   | = = 8                  | <b>\</b>              |                      |                         |             |

|                                               | 9              | Re Ac    | 4 3 4 3                 | 8 10<br>11 14<br>15 21 | 8 1                   |                      |                         |             |

|                                               | \$             | ٦ç       | 61 m 13                 | ~ 2 2                  | 1 ×                   |                      |                         |             |

|                                               | 22             | æ        | 3 4                     | 5 6<br>7 8<br>0 11     | 2 2 7                 |                      |                         |             |

|                                               |                | Re Ac    |                         | 8 10 5                 | = = N                 | 14                   |                         |             |

|                                               | ध              | Re Ac    | 与<br>1<br>2<br>3        | E 20 F                 | 2 2 2                 | <b> </b>             |                         |             |

|                                               | 10             | e Re     |                         | 2 6 8                  | 7 8<br>10 11<br>14 15 | <sup>2</sup> ←       | ***                     |             |

| ection)                                       | 6.5            | Re Ac    | <b>[ 4</b> 4            | N M →                  | 9 8 11                | 12 8 A               |                         |             |

| l is                                          | _              | ٧        | - YY                    | 1 4 W                  | 2 to 12               | <b>≒</b> ≈ \r        | T 4                     |             |

| I mon                                         | 0'7            | Ac Re Ac | 小。                      | 4) = ==                | . w w .~              | 2 7 2                | <b> </b>                |             |

| evels                                         | 2.5            | Re       | 1<br>1<br>1000          | 442                    | S 20 10               | <b>5</b> 11 21       | я <u>/</u>              |             |

| lity L                                        |                | Re Ac    |                         | - 47                   | N W →                 | 9 8 11               | 12 12 A                 |             |

| 8                                             | 1.5            | Re Ac    |                         | [令令                    | ~ ~ ~                 | 2 ~ S                | # # V                   |             |

| Acceptable Quality Levels (normal inspection) | 1.0            | ¥        |                         | か。今                    | \$                    | 3 4 5 6 7 8          | 10 11<br>14 15<br>21 22 |             |

| Ÿ                                             | 0.65           | #        |                         | $\Rightarrow$          | \$\$-                 | 0 4 W                | 8 11 SI                 | <u>'a</u>   |

|                                               |                | Re Ac    |                         |                        | - Y-V                 | N 0 →                | 6 7<br>8 10<br>11 14    | 15.         |

|                                               | 0.40           | ¥        |                         | —¬⁄                    | [ 44]                 | 1 N E                | 8 7 5                   | 14 15       |

|                                               | 0.25           | Ac Re    |                         |                        | ⇒ [4                  | 5>- ~                | 8 c c                   | 11 91       |

|                                               | 0.15           | 2        |                         |                        | $\Rightarrow$ $$      | (44)二                | 0 4 0                   | 8 ~         |

|                                               |                | Re Ac    |                         |                        |                       | 7 / 1                | 2 6 4                   | 9           |

|                                               | 0.10           | Re Ac F  |                         |                        | $\Longrightarrow$     | [令令                  | - 4 6                   | w           |

|                                               | 0.065          | Ac Re    |                         |                        |                       | ⇒:◊                  | \$                      | £           |

|                                               | 0.040          | 光        |                         |                        |                       | $\Rightarrow \bar{}$ | (4) 二                   | e .         |

|                                               |                | Re       |                         |                        |                       |                      | - 1 N                   | 2           |

|                                               | 0.025          | γc       |                         |                        |                       | $\Longrightarrow$    | [令令                     | -           |

|                                               | 0.015          | Ac Re    |                         |                        |                       |                      | ⇒: ⟨=                   |             |

|                                               | 0.010          | 2        |                         |                        |                       |                      | <u>;</u>                |             |

| Ш                                             |                | ¥        |                         |                        | ,                     | r                    | <del>/。</del>           | /           |

|                                               | Sample<br>pize |          | 2 8 9                   | # E 8                  | ននេ                   | 22 82 EE             | 05 88 55<br>152 88 55   | 500         |

| 4                                             | size<br>code   | letter   | < m U                   | O 10 14                | 0 ± ¬                 | × -> ×               | ZAO                     | æ           |

|                                               | <del>-</del>   |          | <u> </u>                | <b></b>                | L                     | <b></b>              | <u> </u>                | <del></del> |

- Use first sampling plus before arrow. If sample size equals, or exceeds, lot or bake size, do 100 percent imported

- Use first sampling plus above arrow.

# **Product Selection Guide - D to A Converters**

# 5. PRODUCT SELECTION GUIDE — D TO A CONVERTERS

| Useful Resolution Setting Time On-Chip (bits) |

|-----------------------------------------------|

| 1 Yes                                         |

| 1 Yes                                         |

| 1                                             |

| 1 Yes                                         |

| 1 Yes                                         |

| 1                                             |

| 1 Yes                                         |

| 1 Yes                                         |

| 0.8 Yes 0.8 Yes                               |

|                                               |

|                                               |

# **Product Selection Guide - A to D Converters**

# 6. PRODUCT SELECTION GUIDE — A TO D CONVERTERS

| Page                        | 31                                              | 47                                      | 77                                       | 87                                       | 77                                       | 87                                       | 77                                       | 87                                    | 97                  | 111                          | 127                  |

|-----------------------------|-------------------------------------------------|-----------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|---------------------------------------|---------------------|------------------------------|----------------------|

| Features                    | Low Cost Dual Purpose A-D/D-A<br>Converter      | Microprocessor, TTL and CMOS compatible | TTL and CMOS compatible<br>Serial Output | TTL and CMOS compatible Serial Output | DVM Logic Subsystem | DVM Logic Subsystem          | Single Channel Codec |

| Temperature<br>Range (°C)   | 0 to +70<br>0 to +70<br>0 to +70<br>-55 to +125 | 0 to +70<br>-55 to +125                 | 0 to +70<br>-45 to +85<br>-55 to +125    | 0 to + 70<br>-45 to +85<br>-55 to +125   | 0 to +70<br>-45 to +85<br>-55 to +125    | 0 to +70<br>-45 to +85<br>-55 to +125    | 0 to +70<br>-45 to +85<br>-55 to +125    | 0 to +70<br>-45 to +85<br>-55 to +125 | 0 to +70            | 0 to +70                     | 0 to +70             |

| On-Chip<br>Ref              | Yes<br>Yes<br>Yes                               | Yes                                     | Yes<br>Yes<br>Yes                        | Yes<br>Yes<br>Yes                        | Yes<br>Yes<br>Yes                        | Yes<br>Yes<br>Yes                        | Yes<br>Yes<br>Yes                        | Yes<br>Yes<br>Yes                     | 1                   |                              | 11                   |

| Conversion Method           | Ramp and Compare                                | Successive Approx.                      | Successive Approx.                       | Tracking                                 | Successive Approx.                       | Tracking                                 | Successive Approx.                       | Tracking                              | Dual Slope          | Dual Slope                   | 11                   |

| Conversion<br>Time (µs)     | 0000<br>0000<br>0000<br>0000                    | 55                                      | 31<br>31<br>31                           |                                          | 51<br>51                                 |                                          | <del>2</del> 5 5 5                       |                                       | 160 ms              | 160 ms<br>160 ms             | 11                   |

| Useful Resolution<br>(bits) | 9788                                            | 80 80                                   | <b>ω</b> ωω                              | ωωω                                      | တတတ                                      | တတတ                                      | 222                                      | 555                                   | 34 Digit BCD        | 31 Digit BCD<br>31 Digit BCD | 11                   |

| Туре                        | ZN425E-6<br>ZN425E-7<br>ZN425E-8<br>ZN425J-8    | ZN427E-8<br>ZN427J-8                    | ZN432CJ-8<br>ZN432BJ-8<br>ZN432J-8       | ZN433CJ-8<br>ZN433BJ-8<br>ZN433J-8       | ZN432CJ-9<br>ZN432BJ-9<br>ZN432J-9       | ZN433CJ-9<br>ZN433BJ-9<br>ZN433J-9       | ZN432CJ-10<br>ZN432BJ-10<br>ZN432J-10    | ZN433CJ-10<br>ZN433BJ-10<br>ZN433J-10 | ZNA116E             | ZNA216E<br>ZNA216J           | ZNPCM1E<br>ZNPCM1J   |

# 7. FERRANTI semiconductors

# **ZN425 Series**

# 8 Bit Monolithic D to A/A to D Converter

#### **FEATURES**

- 8, 7 and 6 bit Accuracy

- 0°C to +70°C (ZN425E Series)

- -55°C to +125°C (ZN425J-8)

- TTL and 5V CMOS Compatible

- Single +5V Supply

- Settling Time (D to A) 1 μsec Typical

- Conversion Time (A to D) 1 msec typical, using ramp and compare.

- Extra Components Required

- D-A: Reference capacitor (direct voltage output through 10 kΩ typ.)

A-D : Comparator, gate, clock and reference capacitor

#### DESCRIPTION

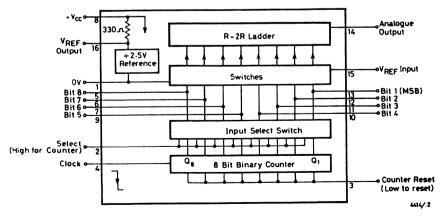

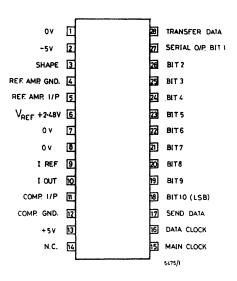

The ZN425 is a monolithic 8-bit digital to analogue converter containing an R-2R ladder network of diffused resistors with precision bipolar switches, and in addition a counter and a 2.5V precision voltage reference. The counter is a powerful addition which allows a precision staircase to be generated very simply merely by clocking the counter.

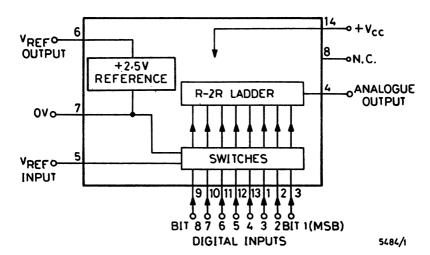

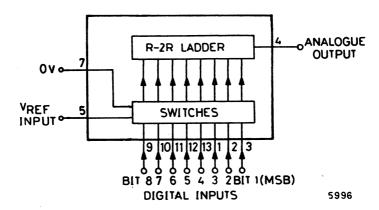

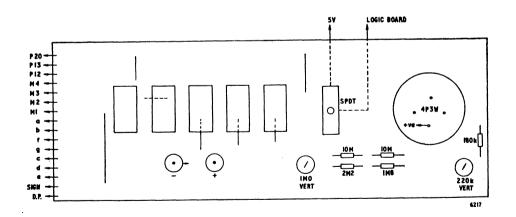

Fig. 1 - System Diagram

#### INTRODUCTION

The ZN425 is an 8-bit dual mode digital to analogue/analogue to digital converter. It contains an 8-bit D to A converter using an advanced design of R-2R ladder network and an array of precision bipolar switches plus an 8-bit binary counter and a 2.5 volt precision voltage reference all on a single monolithic chip.

The special design of ladder network results in full 8-bit accuracy using normal diffused resistors.

The use of the on-chip reference voltage is pin optional to retain flexibility. An external fixed or varying reference may therefore be substituted.

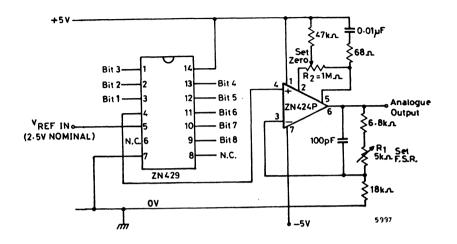

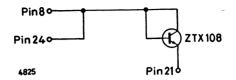

By including on the chip an 8-bit binary counter, analogue to digital conversion can be obtained simply by adding an external comparator (ZN424P) and clock inhibit gating (ZN7400E).

By simply clocking the counter the ZN425 can be used as a self-contained precision ramp generator.

A logic input select switch is incorporated which determines whether the precision switches accept the outputs from the binary counter or external digital inputs depending upon whether the control signal is respectively high or low.

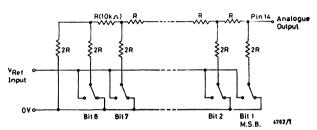

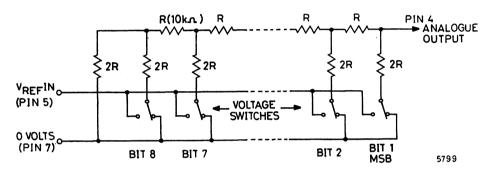

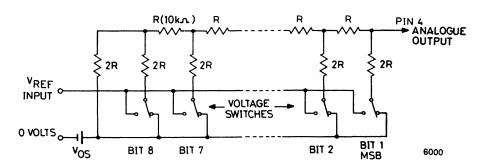

The converter is of the voltage switching type and uses an R-2R resistor ladder network as shown in Fig. 2.

Fig. 2 - The R-2R Ladder Network

Each 2R element is connected either to 0V or V<sub>REF</sub> by transistor switches specially designed for low offset voltage (typically 1 millivolt).

Binary weighted voltages are produced at the output of the R-2R ladder, the value depending on the digital number applied to the bit inputs.

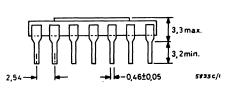

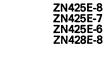

#### ORDERING INFORMATION

| Operating Temperature | 8-bit Accuracy | 7-bit Accuracy | 6-bit Accuracy | Package |

|-----------------------|----------------|----------------|----------------|---------|

| 0°C to +70°C          | ZN425E-8       | ZN425E-7       | ZN425E-6       | Plastic |

| -55°C to +125°C       | ZN425J-8       |                |                | Ceramic |

## **ABSOLUTE MAXIMUM RATINGS**

Supply voltage  $V_{CC}$  ... ... +7.0 volts

Max. voltage, logic and V<sub>RFF</sub> inputs .. .. +5.5 volts See note 3

Operating temperature range ...... 0°C to +70°C (ZN425E Series)

-55°C to +125°C (ZN425J-8)

Storage temperature range ... .. -55°C to +125°C

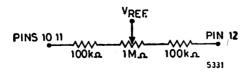

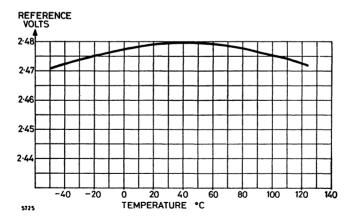

CHARACTERISTICS (at  $T_{amb}=25\,^{\circ}\text{C}$  and  $V_{CC}=+5$  volts unless otherwise specified). Internal voltage reference

| Parameter                                | Symbol           | Min.  | Тур.   | Max. | Units  | Conditions             |

|------------------------------------------|------------------|-------|--------|------|--------|------------------------|

| Output voltage                           | V <sub>REF</sub> | 2 · 4 | 2 · 55 | 2.7  | volts  | I = 7.5  mA (internal) |

| Slope resistance                         | R <sub>s</sub>   |       | 2      | 4    | ohms   | I = 7.5  mA (internal) |

| V <sub>REF</sub> Temperature coefficient |                  | _     | 40     | _    | ppm/°C | I = 7.5  mA (internal) |

Note: The internal reference requires a 0.22 µF stabilising capacitor between pins 1 and 16.

## 8-Bit D to A Converter and Counter

| Parameter                                                        | Symbol          | Min.             | Тур.    | Max.    | Units                        | Conditions                                  |

|------------------------------------------------------------------|-----------------|------------------|---------|---------|------------------------------|---------------------------------------------|

| Resolution                                                       |                 | 8                | _       | _       | bits                         |                                             |

| Accuracy ZN425J-8 (useful ZN425E-8 resolution) ZN425E-7 ZN425E-6 |                 | 8<br>8<br>7<br>6 |         |         | bits<br>bits<br>bits<br>bits | V <sub>REF</sub> Input = 2 to 3V            |

| Non-linearity                                                    |                 |                  | _       | ±0·5    | L.S.B.                       | See Note 3                                  |

| Differential non-linearity                                       |                 | _                | ±0·5    | _       | L.S.B.                       | See Note 6                                  |

| Settling time                                                    |                 | _                | 1 · 0   | _       | με                           | 1 L.S.B. step                               |

| Settling time to 0 · 5 L.S.B.                                    |                 | -                | 1 · 5   | 2.5     | μ <b>s</b>                   | All bits ON toOFF or OFF to ON              |

| Offset voltage ZN425J-8<br>ZN425E-8<br>ZN425E-6<br>ZN425E-7      | Vos             | _                | 8       | 12<br>8 | mV<br>mV                     | All bits OFF<br>See Note 3                  |

| Full scale output                                                |                 | 2 · 545          | 2 · 550 | 2 · 555 | volts                        | All bits ON<br>Ext. V <sub>REF</sub> =2.56V |

| Full scale temperature coeff.                                    |                 | _                | 3       | _       | ppm/°C                       | Ext. V <sub>REF</sub> =2.56V                |

| Non-linearity error temp. coeff.                                 |                 | _                | 7.5     |         | ppm/°C                       | Relative to F.S.R.                          |

| Analogue output resistance                                       | Ro              | _                | 10      | _       | kΩ                           |                                             |

| External reference voltage                                       |                 | 0                |         | 3.0     | volts                        |                                             |

| Supply voltage                                                   | V <sub>CC</sub> | 4.5              | _       | 5.5     | volts                        | See Note 3                                  |

| Supply current                                                   | I <sub>s</sub>  | _                | 25      | 35      | mA                           |                                             |

| High level input voltage                                         | VIH             | 2.0              | _       | _       | volts                        | See Notes 1 and 2                           |

| Low level input voltage                                          | VIL             | _                | _       | 0.7     | volts                        |                                             |

### CHARACTERISTICS (continued).

| Parameter                                             | Symbol          | Min.  | Тур. | Max.          | Units | Conditions                                        |

|-------------------------------------------------------|-----------------|-------|------|---------------|-------|---------------------------------------------------|

| High level input current                              | I <sub>IH</sub> |       | _    | 10            | μΑ    | $V_{CC} = \text{max.}$ $V_{I} = 2.4V$             |

|                                                       |                 | _     | _    | 100           | μΑ    | V <sub>CC</sub> = max.<br>V <sub>I</sub> = 5 · 5V |

| Low level input current, bit inputs                   | I <sub>IL</sub> |       | _    | -0·68         | mA    | $V_{CC} = \text{max.}$ $V_{I} = 0.3V$             |

| Low level input current, clock reset and input select | ار              | _     | _    | <i>-</i> 0·18 | mA    |                                                   |

| High level output current                             | Іон             | _     | _    | -40           | μА    |                                                   |

| Low level output current                              | loL             |       |      | 1 · 6         | mA    |                                                   |

| High level output voltage                             | V <sub>OH</sub> | 2 · 4 | _    | _             | volts | $V_{CC} = min.$ $Q = 1$ $I_{load} = -40 \mu A$    |

| Low level output voltage                              | V <sub>OL</sub> | _     | _    | 0.4           | volts | $V_{CC} = min.$ $Q = 0$ $I_{load} = 1.6 mA$       |

| Maximum counter clock frequency                       | f <sub>c</sub>  | 3     | 5    | _             | MHz   | See Note 5                                        |

| Reset pulse width                                     | t <sub>R</sub>  | 200   | _    | _             | ns    | See Note 4                                        |

#### Notes:

- 1. The Input Select pin (2) must be held low when the bit pins (5, 6, 7, 9, 10, 11, 12 and 13) are driven externally.

- 2. To obtain counter outputs on bit pins the Input Select pin (2) should be taken to  $+V_{CC}$  via a 1 k $\Omega$  resistor.

- 3. The ZN425J differs from the ZN425E in the following respects:

- (a) For the ZN425J, the maximum linearity error may increase to  $\pm 1$  LSB over the temperature ranges –55 °C to 0 °C and +70 °C to +125 °C.

- (b) Maximum operating voltage. Between 70°C and 125°C the maximum supply voltage is reduced to 5.0V.

- (c) Offset voltage. The difference is due to package lead resistance. This offset will normally be removed by the setting up procedure, and because the offset temperature coefficient is low, the specified accuracy will be maintained.

- 4. The device may be reset by gating from its own counter.

- 5. F<sub>max</sub> in A/D mode is 300 kHz, see page 36.

- Monotonic over full operating temperature range at resolution appropriate to accuracy.

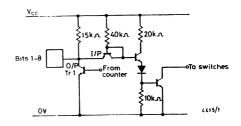

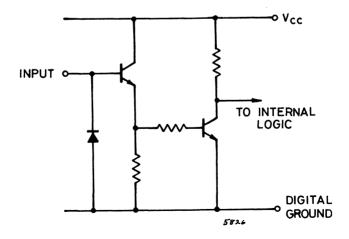

If Pin 2 is high then the output equals the Q output of the corresponding counter.

If Pin 2 is low then the output transistor. Tr1 is held off.

Fig. 3 - Bit Inputs/Outputs

#### APPLICATIONS

#### 1. 8-bit D to A Converter

The ZN425 gives an analogue voltage output directly from pin 14 therefore the usual current to voltage converting amplifier is not required. The output voltage drift, due to the temperature coefficient of the Analogue Output Resistance  $R_o$ , will be less than 0.004% per °C (or 1 L.S.B./ 100°C) if  $R_1$  is chosen to be  $\geqslant 650$  k $\Omega$ .

In order to remove the offset voltage and to calibrate the converter a buffer amplifier is necessary. Fig. 4 shows a typical scheme using the internal reference voltage. To minimise temperature drift in this and similar applications the source resistance to the inverting input of the operational amplifier should be approximately  $6\,\mathrm{k}\Omega$ . The calibration procedure is as follows:

- i. Set all bits to OFF (low) and adjust  $R_2$  until  $V_{out} = 0.000V$ .

- ii. Set all bits to ON (high) and adjust R<sub>1</sub> until V<sub>out</sub> = Nominal full scale reading 1 L.S.B.

- ili. Repeat i. and ii.

e.g. Set F.S.R. to

$$+3.840$$

volts  $-1$  L.S.B.

=  $3.825$  volts

(1 L.S.B. =  $\frac{3.84}{256}$  = 15.0 millivolts.)

Fig. 4 - 8-bit Digital to Analogue Converter

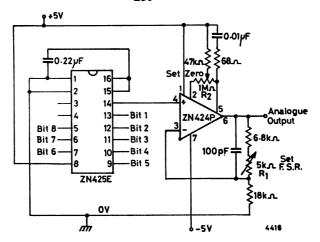

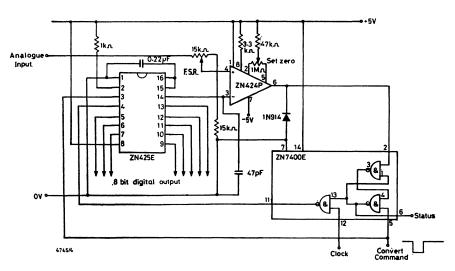

### 2. 8-bit Analogue to Digital Converter

A counter type ADC can be constructed by adding a voltage comparator and a latch as in Fig. 5. On the negative edge of the CONVERT COMMAND pulse (15  $\mu s$  minimum) the counter is set to zero and the STATUS latch to logical 1. On the positive edge the gate is opened, enabling clock pulses to be fed to the counter input of the ZN425. The minimum negative clock pulse width to the ZN425 is 100 ns. The analogue output of the ZN425 ramps until it equals the voltage on the other input of the comparator. At this point the comparator output goes low and resets the STATUS latch to inhibit further clock pulses. The logical 0 from the status latch indicates that the 8 bit digital output is a valid representation of the analogue input voltage.

A small capacitor of 47 pF is added to the ZN425 output to stop any positive going glitches prematurely resetting the status latch. This capacitance is in parallel with the ZN425 output capacitance (20–30 pF) and they form a time constant with the ZN425 output resistance (10 k $\Omega$ ). This time constant is the main limit to the maximum clock frequency. With a fast comparator the clock frequency can be up to 300 kHz. Using the ZN424P as a comparator the clock frequency should be restricted to 100 kHz. The conversion time varies with the input, being a maximum for full scale input.

Maximum conversion time =

$$\frac{256}{\text{clock frequency in Hz}}$$

seconds

Fig. 5 – 8-bit Analogue to Digital Converter

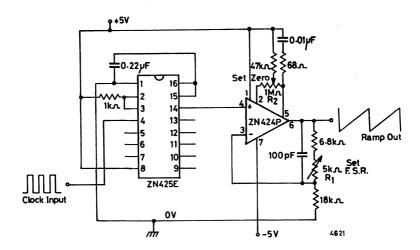

#### 3. Precision Ramp Generator

The inclusion of an 8-bit binary counter on the chip gives the ZN425 a useful ramp generator function. The circuit, Fig. 6 uses the same buffer stages as the D to A converter. The calibration procedure is also the same. Holding pin 2 low will set all bits to ON and if RESET is taken low with pin 2 high all the bits are turned OFF. If the end voltages of the ramp are not required to be set accurately then the buffer stage could be omitted and the voltage ramp will appear directly at pin 14.

Fig. 6 - Precision Ramp Generator

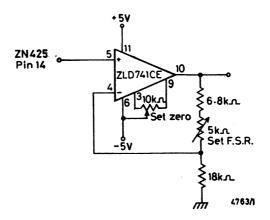

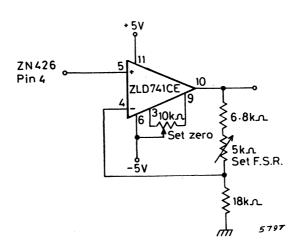

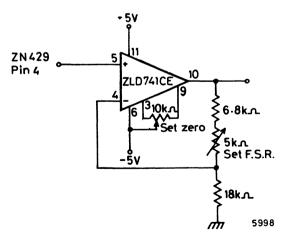

## 4. Alternative Output Buffer using the ZLD741

The following circuit, employing the ZLD741 operational amplifier, may be used as the output buffer for both the 8-bit Digital to Analogue Converter (Fig. 4) and the Precision Ramp Generator (Fig. 6).

Fig. 7 - The ZLD741 as Output Buffer

## 5. Further Applications

Details of a wide range of additional applications, described in the Ferranti publication 'Application Report-ZN425 8-bit A-D/D-A Converter', are also available.

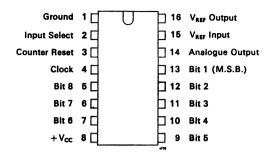

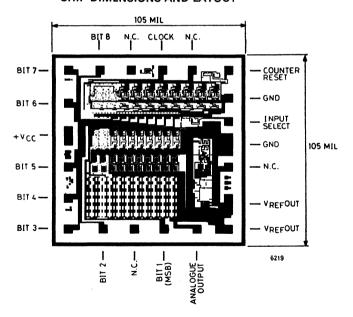

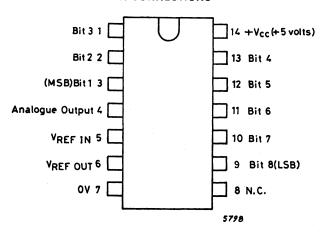

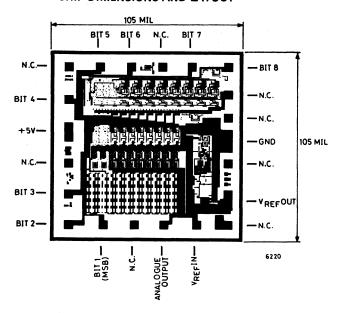

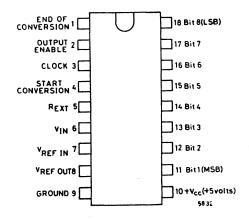

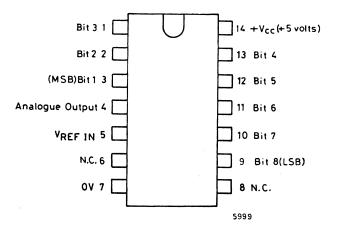

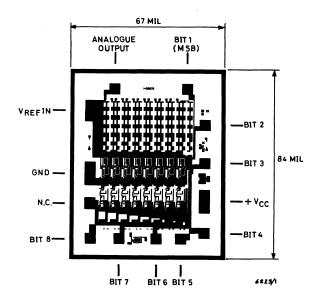

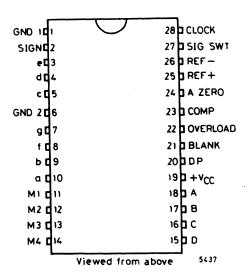

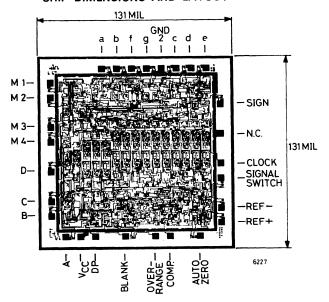

### **PIN CONNECTIONS**

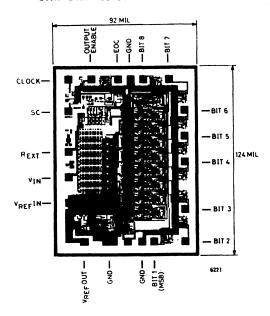

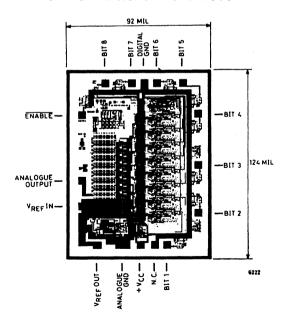

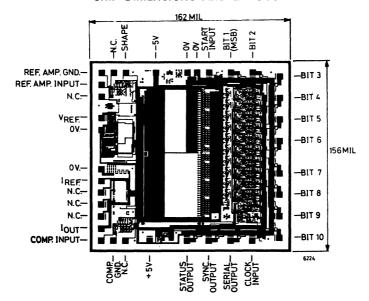

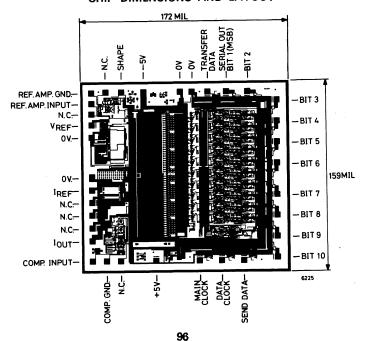

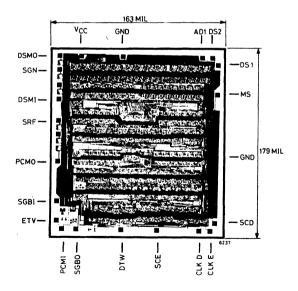

## CHIP DIMENSIONS AND LAYOUT

## 8 Bit Monolithic D to A Converter

#### **FEATURES**

- 8, 7 and 6-bit Accuracy

- ZN426E Series Commercial Temp. Range 0°C to +70°C

- ZN426J-8 Military Temp. Range -55°C to +125°C

- TTL and 5V CMOS Compatible

- Single +5V Supply

- Settling Time 1 μsec. Typical

- Only Reference Capacitor and Resistor required

#### **DESCRIPTION**

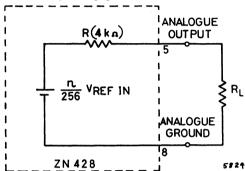

The ZN426 is a monolithic 8-bit digital to analogue converter containing an R-2R ladder network of diffused resistors with precision bipolar switches and a 2.5V precision voltage reference.

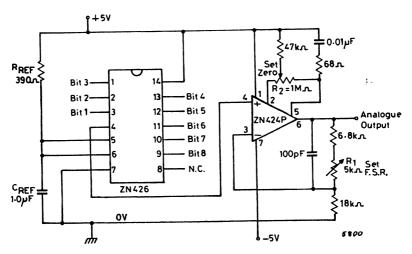

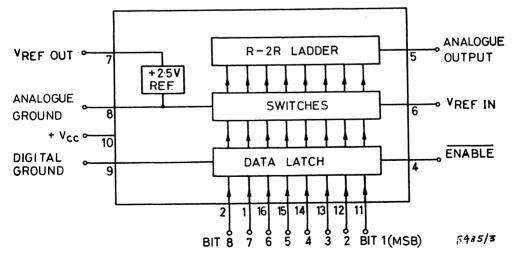

Fig. 1. System Diagram

#### INTRODUCTION

The ZN426 is an 8-bit digital to analogue converter. It contains an advanced design of R-2R ladder network and an array of precision bipolar switches plus a 2.5 volt precision voltage reference all on a single monolithic chip.

The special design of ladder network results in full 8-bit accuracy using normal diffused resistors.

The use of the on-chip reference voltage is pin optional to retain flexibility. An external fixed or varying reference may therefore be substituted. In this case there is no need to supply power to the internal reference so  $R_{REF}$  and  $C_{REF}$  can be omitted.

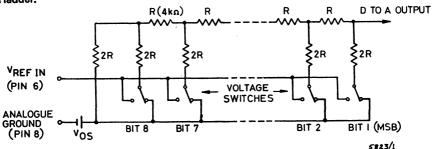

The converter is of the voltage switching type and uses an R-2R resistor ladder network as shown in Fig. 2.

Fig. 2. The R-2R Ladder Network

Each 2R element is connected either to 0V or V<sub>REF</sub> by transistor switches specially designed for low offset voltage (typically 1 millivolt).

Binary weighted voltages are produced at the output of the R-2R ladder, the value depending on the digital number applied to the bit inputs.

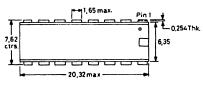

#### ORDERING INFORMATION

| Operating Temperature | 8-bit accuracy | 7-bit accuracy | 6-bit accuracy | Package |

|-----------------------|----------------|----------------|----------------|---------|

| 0 to +70°C            | ZN426E-8       | ZN426E-7       | ZN426E-6       | Plastic |

| -55 to +125°C         | ZN426J-8       |                | _              | Ceramic |

#### **ABSOLUTE MAXIMUM RATINGS**

Supply voltage  $V_{CC}$  ... .. ... ... +7.0 volts Max. voltage, logic and  $V_{REF}$  inputs ... ... +5.5 volts Storage temperature range ... ... ... -55 to +125°C

ELECTRICAL CHARACTERISTICS ( $V_{CC} = +5 \text{ volts}, T_{amb} = 25 ^{\circ}\text{C}$  unless otherwise specified).

| Parameter                                                   | Symbol          | Min.        | Тур.       | Max.       | Units                | Conditions                                       |

|-------------------------------------------------------------|-----------------|-------------|------------|------------|----------------------|--------------------------------------------------|

| Converter<br>Resolution                                     |                 | 8           |            |            | bits                 |                                                  |

| Accuracy (useful resolution)                                |                 | 8<br>7<br>6 | _          |            | bits<br>bits<br>bits | V <sub>REF</sub> input<br>=2.0 to 3.0 volts      |

| Non-linearity                                               |                 |             |            | ±0.5       | L.S.B.               | Note 1                                           |

| Differential non-linearity                                  |                 |             | ±0.5       |            | L.S.B.               | Note 2                                           |

| Settling time to 0.5 L.S.B.                                 |                 | _           | 1.0        | _          | μs                   | 1 L.S.B. step                                    |

| Settling time to 0.5 L.S.B.                                 |                 |             | 2.0        | _          | μs                   | All bits ON to OFF or OFF to ON                  |

| Offset voltage ZN426J-8<br>ZN426E-8<br>ZN426E-7<br>ZN426E-6 | V <sub>os</sub> | _           | 5.0<br>3.0 | 8.0<br>5.0 | mV<br>mV             | All bits OFF<br>Note 1                           |

| V <sub>OS</sub> temperature coefficient                     |                 | _           | 5          |            | μV/°C                |                                                  |

| Full scale output                                           |                 | 2.545       | 2.550      | 2.555      | volts                | All bits ON<br>Ext. V <sub>REF</sub> =<br>2.560V |

| Full scale temp. coefficient                                |                 | _           | 3          | _          | ppm/°C               | Ext. V <sub>REF</sub> = 2.560V                   |

| Non-linearity temp. coeff.                                  |                 | _           | 7.5        | _          | ppm/°C               | Relative to F.S.R.                               |

#### Notes:

- 1. The ZN426J-8 differs from the ZN426E-8 in the following respects:

- (a) For the ZN426J-8, the maximum linearity error may increase to  $\pm 0.4\%$  FSR i.e.  $\pm 1$  LSB over the temperature ranges  $-55^{\circ}$ C to  $0^{\circ}$ C and  $+70^{\circ}$ C to  $+125^{\circ}$ C.

- (b) Offset voltage. The difference is due to package lead resistance. This offset will normally be removed by the setting up procedure, and because the offset temperature coefficient is low, the specified accuracy will be maintained.

- 2. Monotonic over full temperature range at resolution appropriate to accuracy.

### **ELECTRICAL CHARACTERISTICS** (continued)

| Parameter                                       | Symbol           | Min.  | Тур. | Max.  | Units  | Conditions                                       |

|-------------------------------------------------|------------------|-------|------|-------|--------|--------------------------------------------------|

| Analogue output resistance                      | R <sub>o</sub>   | _     | 10   | _     | kΩ     |                                                  |

| External reference voltage                      |                  | 0     | _    | 3.0   | volts  |                                                  |

| Supply voltage                                  | V <sub>cc</sub>  | 4.5   | _    | 5.5   | Volts  |                                                  |

| Supply current                                  | l <sub>s</sub>   | _     | 5    | 9     | mA     |                                                  |

| High level input voltage                        | VIH              | 2.0   | _    | _     | volts  |                                                  |

| Low level input voltage                         | VIL              | _     | _    | 0.7   | volts  |                                                  |

| High level input current                        | I <sub>IH</sub>  | _     | _    | 10    | μΑ     | $V_{CC} = max.,$ $V_{I} = 2.4V$                  |

|                                                 |                  | _     | _    | 100   | μΑ     | V <sub>CC</sub> = max.,<br>V <sub>I</sub> = 5.5V |

| Low level input current                         | IIL              | _     | _    | -0.18 | mA     | $V_{CC} = max.,$<br>$V_{I} = 0.3V$               |

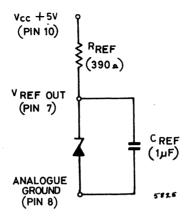

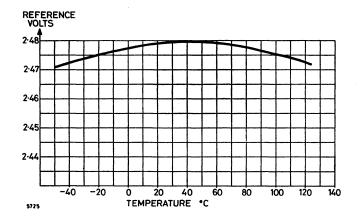

| Internal Voltage<br>Reference<br>Output voltage | V <sub>REF</sub> | 2.475 | 2.55 | 2.625 | volts  | <i>Note</i> * R <sub>REF</sub> = 390Ω            |

| Slope resistance                                | R <sub>s</sub>   | _     | 1    | 2     | ohms   | $R_{REF} = 390\Omega$                            |

| V <sub>REF</sub> temperature coefficient        |                  | _     | 40   | _     | ppm/°C | $R_{REF} = 390\Omega$                            |

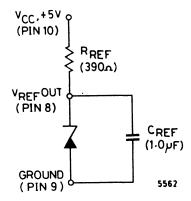

Note\* The internal reference requires a 1  $\mu$ F stabilising capacitor between pins 7 and 6 (C<sub>REF</sub>) and a 390Ω resistor between pins 14 and 6 (R<sub>REF</sub>).

#### **APPLICATIONS**

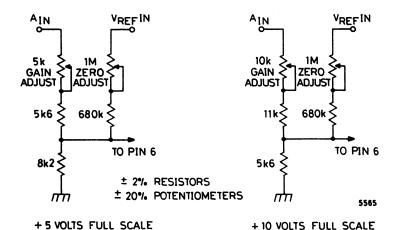

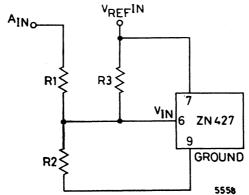

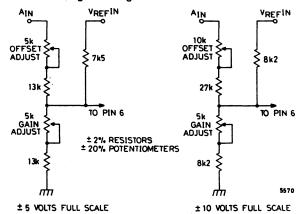

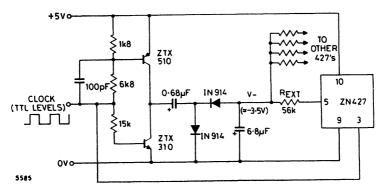

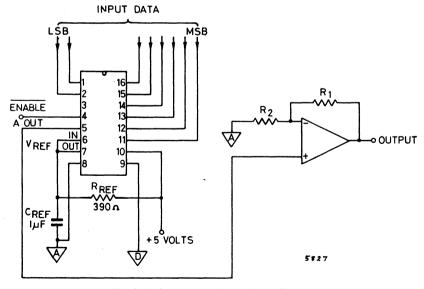

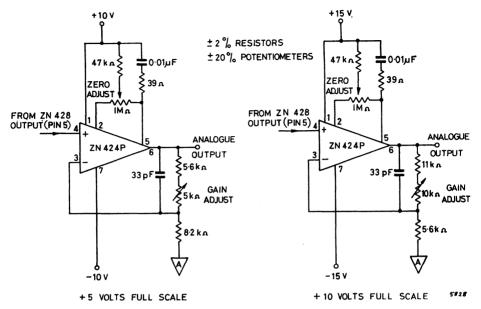

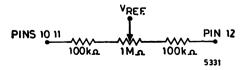

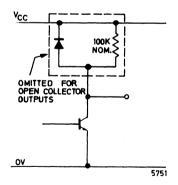

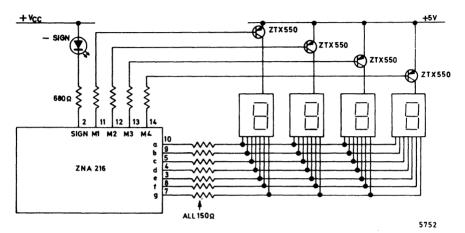

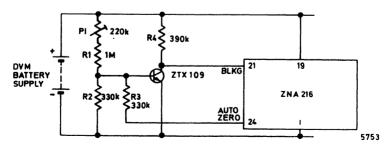

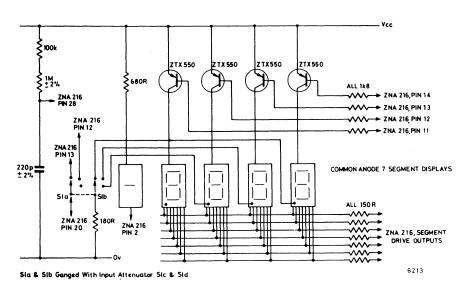

#### 1. 8-bit D to A Converter